INFRA

INFRA

INFRA

INFRA

INFRA

INFRA

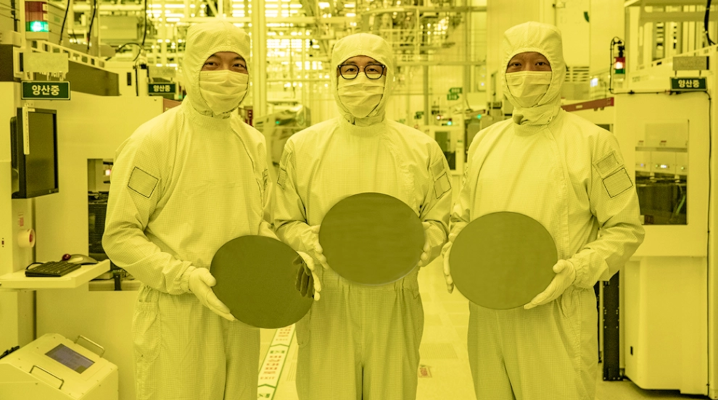

In a major industry milestone, Samsung Electronics Co. Ltd. today announced that it has begun producing chips using its latest three-nanometer semiconductor manufacturing process.

The process will facilitate the creation of faster, more power-efficient chips. It’s also significant for another reason. Samsung’s new process is the first implementation of gate-all-around, or GAA, technology, a new way of designing transistors that’s expected to become an industry standard in the coming years.

A chip processes data in the form of ones and zeros. At the hardware level, ones and zeros are represented as electricity. This electricity, in turn, is manipulated by the chip’s transistors to carry out calculations.

A transistor consists of two main components: a channel and a gate. The GAA technology that powers Samsung’s three-nanometer process introduces major improvements to both components.

A transistor’s channel is a tiny conductive wire through which electricity can travel. The gate, in turn, is a component capable of changing the way that electricity travels through the channel. The changes that the gate makes to the movement of electricity are what switch the state of the transistor from 1 to 0 and vice versa.

The transistors in current chips are based on an industry-standard design known as FinFET. In a FinFET transistor, the channel is partly surrounded by the gate. In the GAA design that Samsung has adopted for its three-nanometer process, the gate surrounds the channel not partly but fully.

GAA technology has several major advantages over FinFET. One of the main ways that chipmakers develop faster processors is by shrinking their transistors. FinFET technology has certain limitations that are making it increasingly difficult to shrink transistors, which in turn is limiting chipmakers’ ability to build faster processors. GAA technology addresses many of FinFET’s limitations, thereby making it easier to develop better chips.

Another benefit of GAA technology is customizability. Some devices require chips optimized for performance, while others prioritize power efficiency over speed. One of the main factors that influence a chip’s performance and power efficiency is the width of its transistors’ channels. GAA technology makes it possible to modify the channel width, which means that chipmakers can customize their processors for different devices’ speed and energy usage requirements.

Samsung is one of several chipmakers adopting the GAA design. In Samsung’s implementation of the technology, the transistor channel comprises a series of conductive nanosheets placed one atop another. The gate, the component that switches the transistor from 1 to 0 and vice versa, fully surrounds each nanosheet.

Samsung says that chips produced using its three-nanometer process can provide 45% better power efficiency than current five-nanometer silicon. Additionally, the technology will make it possible to increase processing speeds by up to 23%.

Samsung reportedly plans to launch a second, improved iteration of its new process in 2023. The second-generation process is expected to be 50% more power-efficient than five-nanometer technology. Samsung also stated that customers can expect a 30% performance improvement.

Support our mission to keep content open and free by engaging with theCUBE community. Join theCUBE’s Alumni Trust Network, where technology leaders connect, share intelligence and create opportunities.

Founded by tech visionaries John Furrier and Dave Vellante, SiliconANGLE Media has built a dynamic ecosystem of industry-leading digital media brands that reach 15+ million elite tech professionals. Our new proprietary theCUBE AI Video Cloud is breaking ground in audience interaction, leveraging theCUBEai.com neural network to help technology companies make data-driven decisions and stay at the forefront of industry conversations.