INFRA

INFRA

INFRA

INFRA

INFRA

INFRA

Intel Corp. has integrated virtual radio access network acceleration into its latest 4th Gen Intel Xeon system-on-chip, helping network operators gear up their efforts to deliver cloud-native features for next-generation 5G core and edge networks.

The announcement came today at the MWC event, formerly known as Mobile World Congress, in Barcelona. Intel said it’s just the latest step in its mission to virtualize the world’s networks, including core, open RAN and edge.

Network virtualization involves combining hardware and software network resources and features into a single, software-based administrative entity. It’s a key capability for communication service providers as they migrate from fixed-function hardware to programmable, software-defined platforms that provide more agility and greater cost efficiency.

According to Intel, this demand for agile, high-performance and scalable networks requires the adoption of fully virtualized, software-based platforms that can run on general-purpose processors. However, network operators need to accelerate network virtualization to get the most out of these new architectures, and that’s where Intel believes it can make its mark.

Intel said its 4th Gen Intel Xeon Scalable processors with Intel vRAN Boost come with expansive industry support from companies that include Advantech Co., Ltd., Capgemini Inc., Canonical Ltd., Dell Technologies Inc., Telefonaktiebolaget LM Ericsson, Super Micro Computer Inc., Red Hat Inc., Verizon Communications Inc. and Vodafone Ltd. among others. By fully integrating vRAN acceleration into its SoC, Intel says, it eliminates the need for an external accelerator card. Normally, Open RAN network operators rely on external hardware acceleration cards designed to boost the capabilities of silicon processors for network functions.

Intel says that’s no longer necessary. With Intel vRAN Boost, it says it can deliver twice the capacity gains over its previous-generation silicon within the same power envelope, with an additional 20% in power savings that result from the integrated acceleration. So the chips go above and beyond the 4th Gen Intel Xeon platform’s standard performance-per-watt, bettering the performance of the most powerful Layer 1 SoC accelerator cards available today, Intel said.

To prove its point, Intel demonstrated at MWC how its Xeon Scalable processors with vRAN Boost were able to deliver an industry-first 1-terabyte-per-second performance for 5G user plane function workloads within a dual-socket server validated by Samsung Electronics Co. Ltd.

Sachin Katti, senior vice president and general manager of Intel’s Network and Edge Group, said the company’s experience in powering the world’s clouds and networks gives it a unique insight on where to place compute and acceleration within the cloud-to-edge continuum.

“The advancements we’ve made in our 4th Gen Intel Xeon platforms to double vRAN performance while staying within the same power envelope, to nearly doubling the 5G core UPF throughput, and to speed the deployment of a wide range of network, security and enterprise edge services, makes Intel the platform for our customers to modernize and monetize their networks of the future,” he said.

In addition, Intel announced new Infrastructure Power Manager for 5G Core reference software that’s designed to work with vRAN Boost. It said the software helps to dynamically match run-time server power consumption with data traffic, without hurting throughput, latency and packet drop, to achieve further efficiency and performance gains.

In a series of tests with networks built by Casa Systems Inc., NEC Corp. and Nokia Corp., Intel demonstrated how it was able to reduce time to market for independent service vendors and network operators by simplifying access to key functions within its 3rd and 4th Gen Xeon Scalable processors, including power telemetry, granular power control states and low-latency frequency change. Customers can therefore use the Infrastructure Power Manager for 5G Core software to reduce the total cost of ownership of their networks and accelerate their progress towards their net zero emission goals, Intel said.

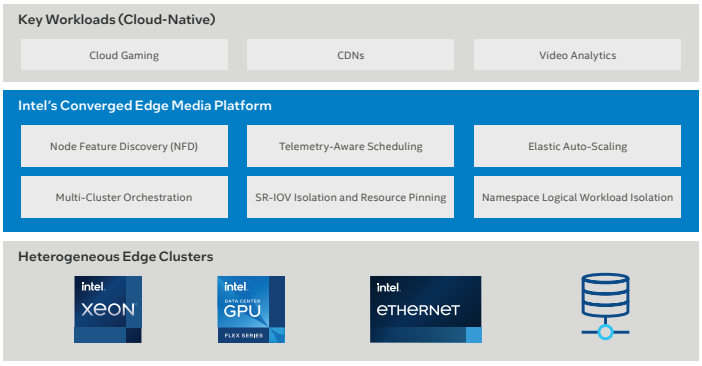

In a second announcement, Intel showcased its new Intel Converged Edge Media Platform, which is designed to deliver multiple video services from a shared multitenant architecture, leveraging cloud-native scalability to respond to shifting demands intelligently.

Video services are driving rapid growth at the network edge, Intel explained. As a result, network operators are making big investments in dedicated resources for each type of video service they deliver, including content delivery networks, cloud gaming, mixed reality, 3D rendering and so on. But this is a risky strategy, Intel believes, because it’s not clear which of these services ultimately will catch on.

The solution, Intel says, is to install a converged platform that can support all of the above use cases through a single, CPU- and GPU-accelerated cloud-native environment. Operators can then use a general-purpose architecture that can change and resize workloads on the fly, enabling all of their video services to reside together.

Lastly, Intel announced an expanded range of Agilex 7 field-programmable gate arrays and eASIC N5X structured application-specific integrated circuits designed for individual cloud, communications and embedded applications.

The new Intel Agilex 7 FPGA AGI 041 devices are designed to support the transition from 200G to 400G networks, Intel said. FPGA’s are a special kind of computer chip that can be reprogrammed for specific tasks on the fly.

Intel says the AGI 041 devices will deliver a balance of capacity, power efficiency and performance for 400G infrastructure processing units and network systems. Meanwhile, the new eASIC N5X080 chips are designed to help network operators optimize cost and power across individual applications, providing 60% greater energy-efficiency versus standard FPGAs, the company said. ASICs are integrated circuit chips customized for a particular use case. They offer performance benefits over flexibility, since they cannot be reprogrammed.

Support our mission to keep content open and free by engaging with theCUBE community. Join theCUBE’s Alumni Trust Network, where technology leaders connect, share intelligence and create opportunities.

Founded by tech visionaries John Furrier and Dave Vellante, SiliconANGLE Media has built a dynamic ecosystem of industry-leading digital media brands that reach 15+ million elite tech professionals. Our new proprietary theCUBE AI Video Cloud is breaking ground in audience interaction, leveraging theCUBEai.com neural network to help technology companies make data-driven decisions and stay at the forefront of industry conversations.